전자제품의 설계는 회로도 작성부터 PCB 레이아웃, 배선까지 이루어집니다. 이 분야의 업무 경험 부족으로 인해 다양한 실수가 자주 발생하여 후속 작업에 지장을 주며, 심한 경우 제작된 회로 기판을 전혀 사용할 수 없게 됩니다. 그러므로 우리는 이 분야에 대한 지식을 향상시키고 모든 종류의 실수를 피하기 위해 최선을 다해야 합니다.

이 기사에서는 나중에 동일한 구덩이를 밟지 않도록 PCB 드로잉 보드를 사용할 때 일반적인 드릴링 문제를 소개합니다. 드릴링은 관통 홀, 막힌 홀, 매설 홀의 세 가지 범주로 구분됩니다. 관통 구멍에는 플러그인 구멍(PTH), 나사 위치 결정 구멍(NPTH), 블라인드 구멍, 매립 구멍, 비아 구멍(VIA)이 포함되며 모두 다층 전기 전도 역할을 합니다. 구멍 유형에 관계없이 구멍 누락 문제로 인해 전체 제품 배치를 직접 사용할 수 없게 됩니다. 따라서 드릴링 설계의 정확성이 특히 중요합니다.

PCB 보드 설계 측면의 구덩이 및 누수 사례 설명

문제 1: Altium이 디자인한 파일 슬롯이 잘못 배치되었습니다.

문제에 대한 설명: 슬롯이 없어 제품을 사용할 수 없습니다.

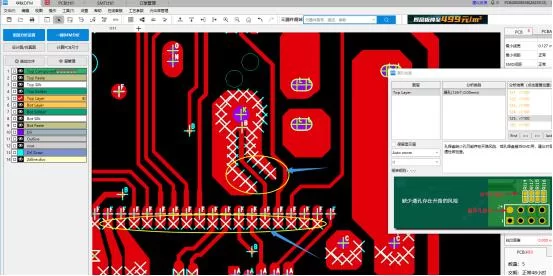

이유분석: 디자인 엔지니어가 패키지를 만들 때 USB 장치용 슬롯을 놓쳤습니다. 그는 보드를 그릴 때 이 문제를 발견했을 때 패키지를 수정하지 않고 홀 심볼 레이어에 슬롯을 직접 그렸습니다. 이론상으로는 이 작업에 큰 문제가 없으나, 제조과정에서 드릴링 레이어만 사용하여 드릴링을 하기 때문에 다른 레이어의 슬롯 존재를 무시하기 쉬우며, 이로 인해 이 슬롯의 드릴링이 누락되어 제품을 사용할 수 없게 됩니다. 아래 그림을 참조하십시오.

구덩이를 피하는 방법: OEM PCB 설계 파일의 각 레이어에는 각 레이어의 기능이 있습니다. 드릴 구멍과 슬롯 구멍은 드릴 레이어에 배치해야 하며 디자인을 제작할 수 있다고 간주할 수 없습니다.

질문 2: 홀 0 D 코드를 통한 Altium 설계 파일;

문제에 대한 설명: 누출은 개방적이고 비전도성입니다.

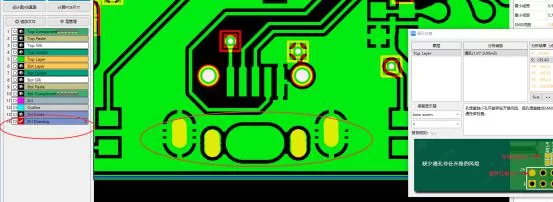

원인분석: 그림 1을 참조하세요. 설계 파일에 누출이 있으며 DFM 제조 적합성 검사 중에 누출이 표시됩니다. 누수 원인을 확인한 결과 알티움 소프트웨어에서 구멍의 직경이 0이어서 설계 파일에는 구멍이 없는 것으로 나타났다(그림 2 참조).

이런 누수 구멍이 생긴 이유는 설계 엔지니어가 구멍을 뚫을 때 실수를 했기 때문입니다. 이 누수 구멍의 문제점을 확인하지 않으면 설계 파일에서 누수 구멍을 찾기가 어렵습니다. 누출 구멍은 전기적 고장에 직접적인 영향을 미치며 설계된 제품을 사용할 수 없습니다.

구덩이를 피하는 방법: DFM 제조 가능성 테스트는 회로도 설계가 완료된 후에 수행되어야 합니다. 누출된 비아는 설계 중 제조 및 생산 과정에서 발견될 수 없습니다. 제조 전 DFM 제조 가능성 테스트를 통해 이 문제를 피할 수 있습니다.

그림 1: 디자인 파일 유출

그림 2: Altium 조리개는 0입니다.

질문 3: PADS에서 디자인한 파일 비아는 출력할 수 없습니다.

문제에 대한 설명: 누출은 개방적이고 비전도성입니다.

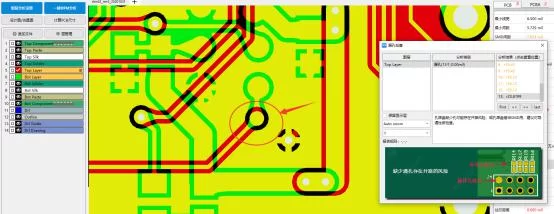

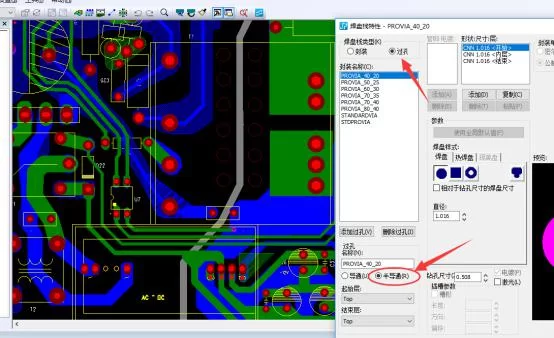

원인분석: 그림 1을 참조하십시오. DFM 제조 가능성 테스트를 사용할 때 누출이 많이 있음을 나타냅니다. 누수 문제의 원인을 확인한 결과, PADS의 비아 중 하나가 반도전 홀로 설계되어 설계 파일에서 반도전 홀이 출력되지 않아 누수가 발생하게 되었습니다(그림 2 참조).

양면 패널에는 반도체 구멍이 없습니다. 엔지니어는 설계 중에 비아 홀을 반도체 홀로 잘못 설정했고, 출력 드릴링 중에 출력 반도체 홀이 누출되어 홀이 누출되는 결과를 낳았습니다.

구덩이를 피하는 방법: 이런 종류의 오작동은 찾기가 쉽지 않습니다. 설계가 완료된 후에는 DFM 제조성 분석 및 검사를 실시하고 제조 전에 문제점을 찾아 누출 문제를 방지해야 합니다.

그림 1: 디자인 파일 유출

그림 2: PADS 소프트웨어 이중 패널 비아는 반도체 비아입니다.